# COMP 122/L Lecture 24

Kyle Dewey

### Outline

• D flip-flops

### Sequential Circuits

### Motivation

#### Output = Input1 + Input2

### Motivation

#### Output = Input1 + Input2

mov r0, #5 add r1, r0, r0

Outputs entirely determined by the inputs

Outputs entirely determined by the inputs

Output = Input1 + Input2

Outputs entirely determined by the inputs

Output = Input1 + Input2

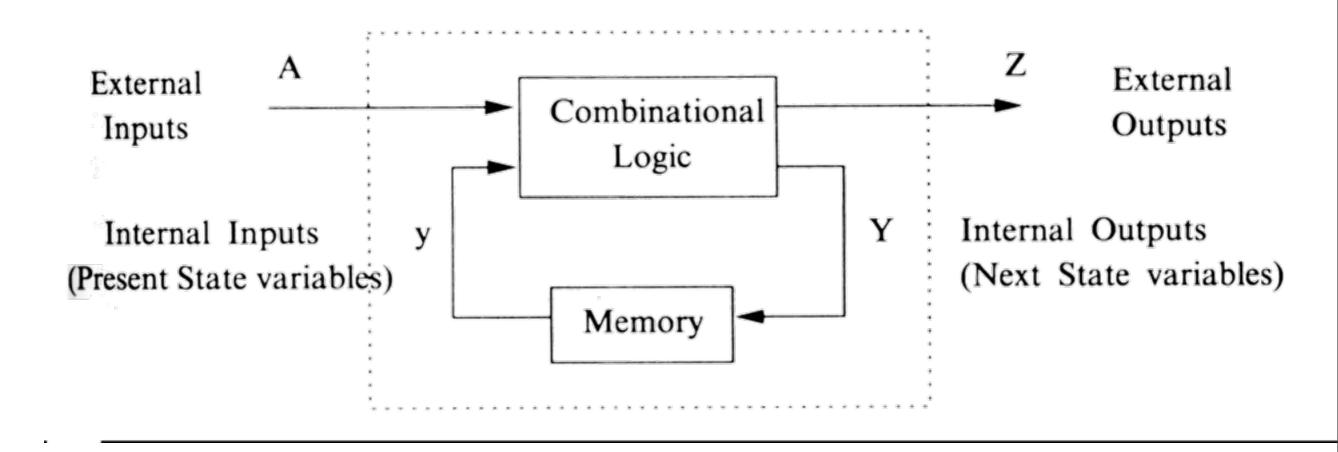

# Sequential Logic

Outputs determined by the inputs, along with the **current state**

Outputs entirely determined by the inputs

Output = Input1 + Input2

#### Sequential Logic Outputs determined by the inputs, along with the current state

mov r0, #5 add r1, r0, r0

# Saving Bits

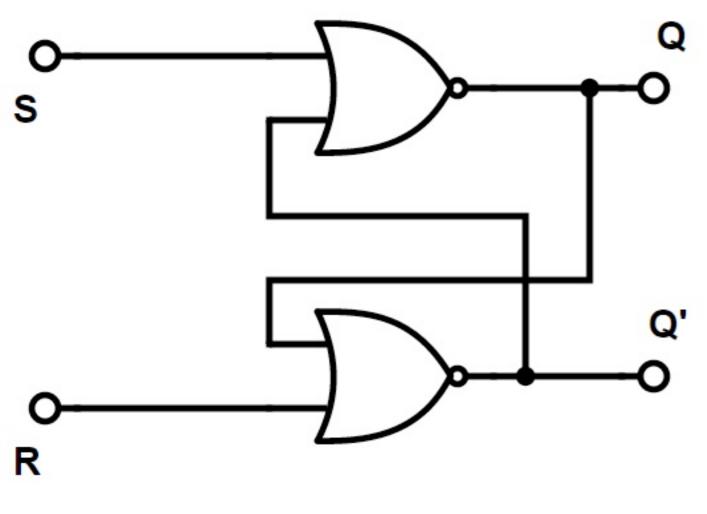

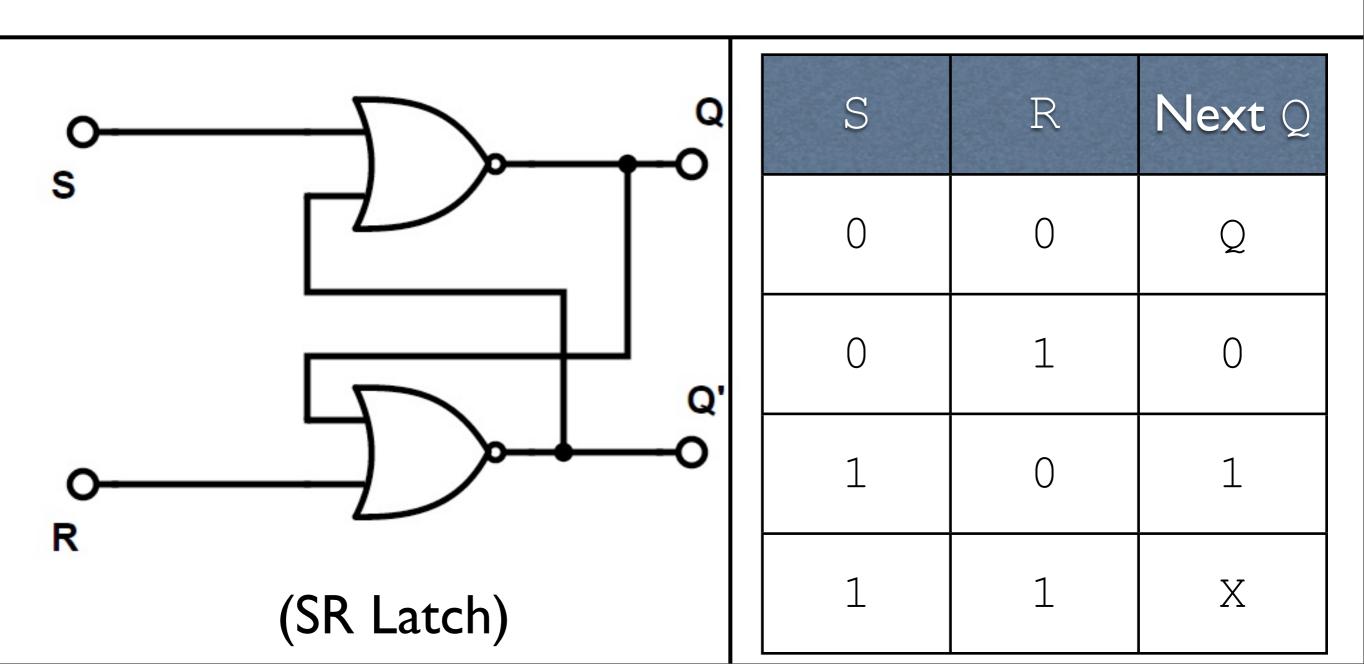

We can utilize feedback: putting the output of the circuit back into itself.

# Saving Bits

We can utilize *feedback*: putting the output of the circuit back into itself.

(SR Latch)

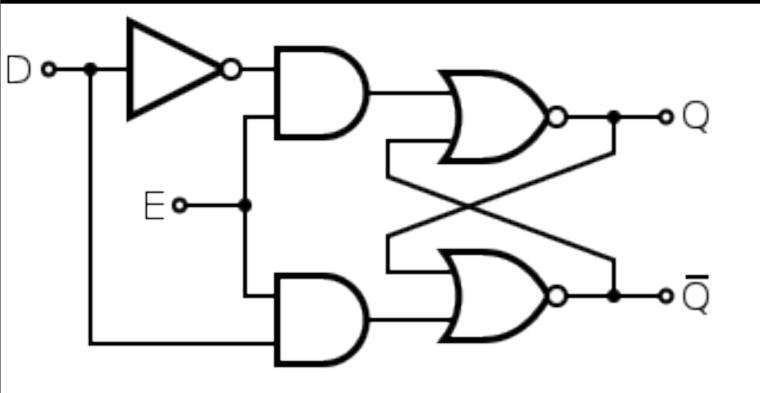

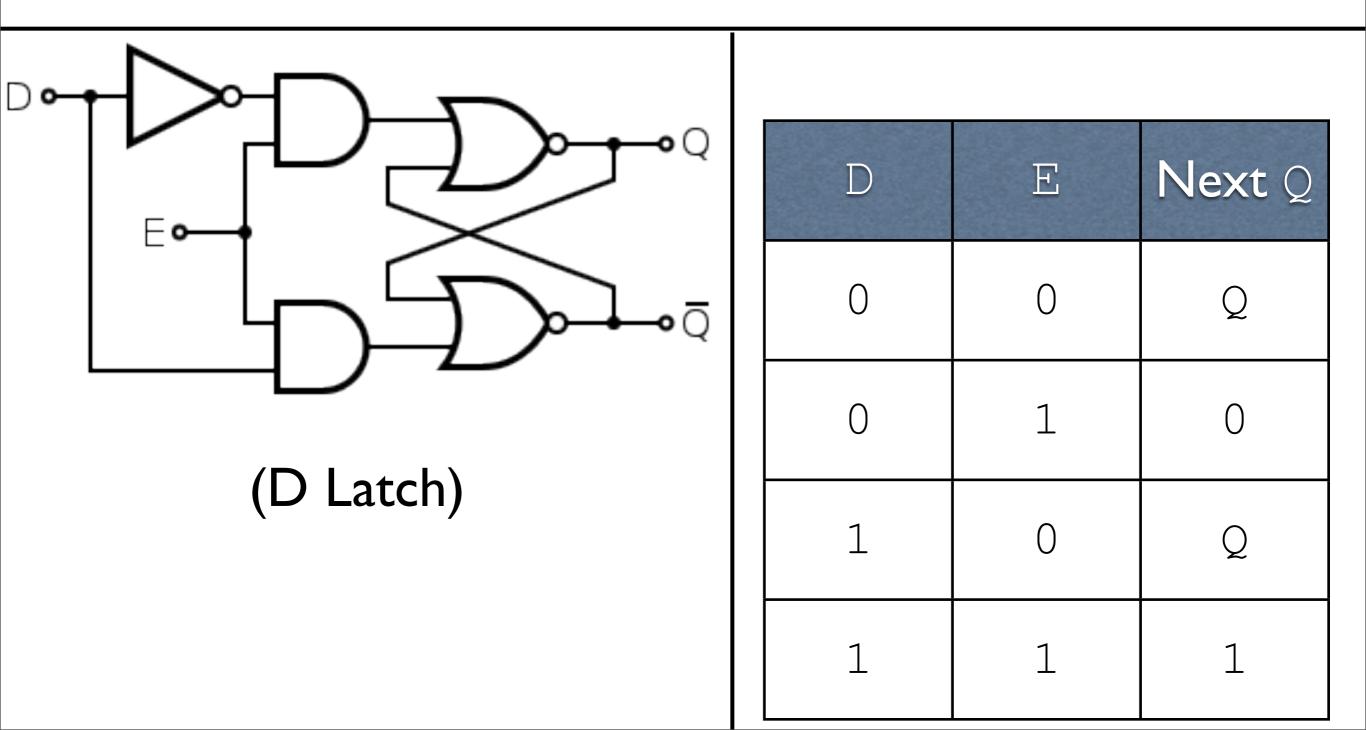

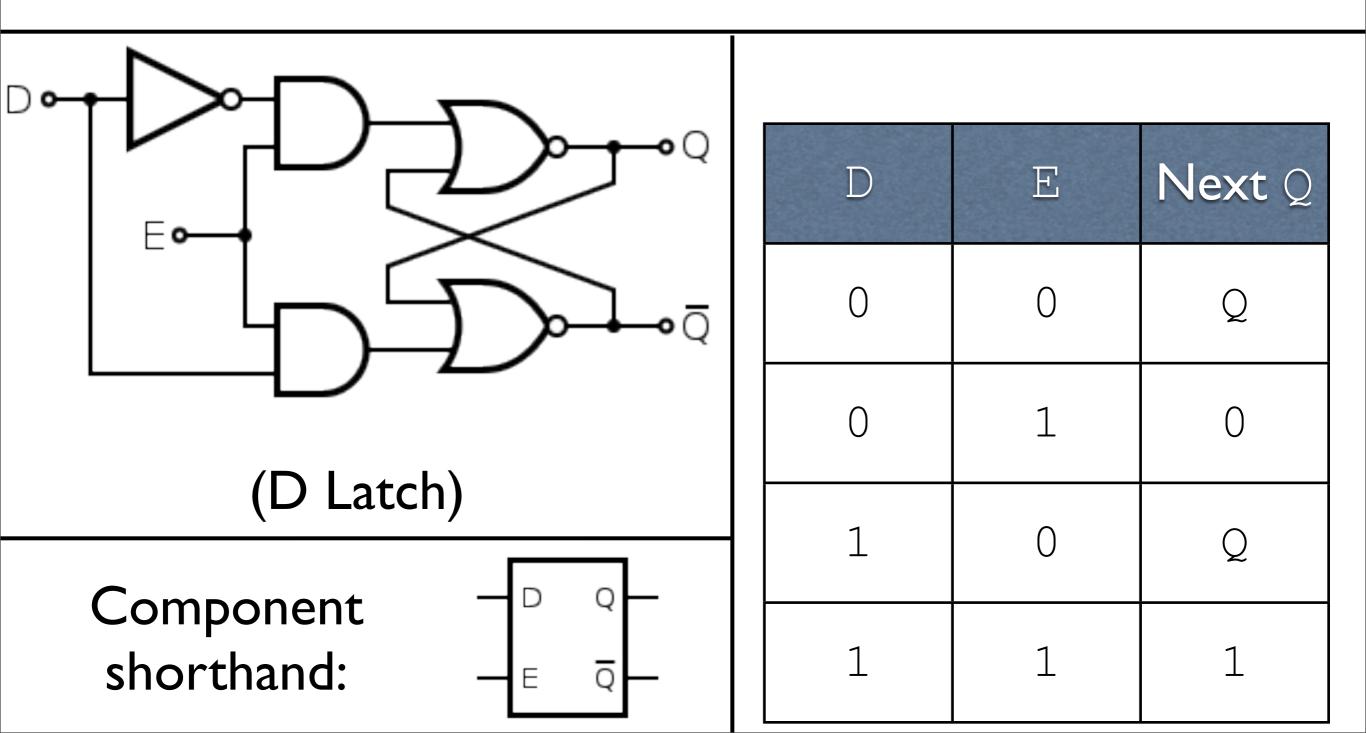

# Saving Bits

We can utilize *feedback*: putting the output of the circuit back into itself.

(D Latch)

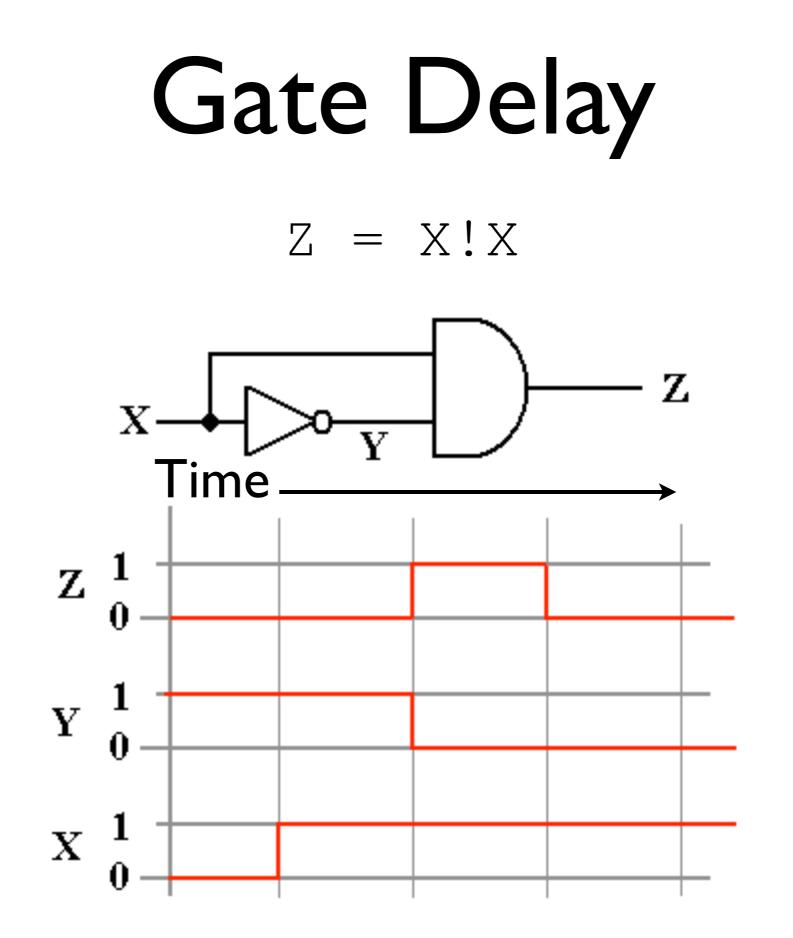

### Question How fast can this go?

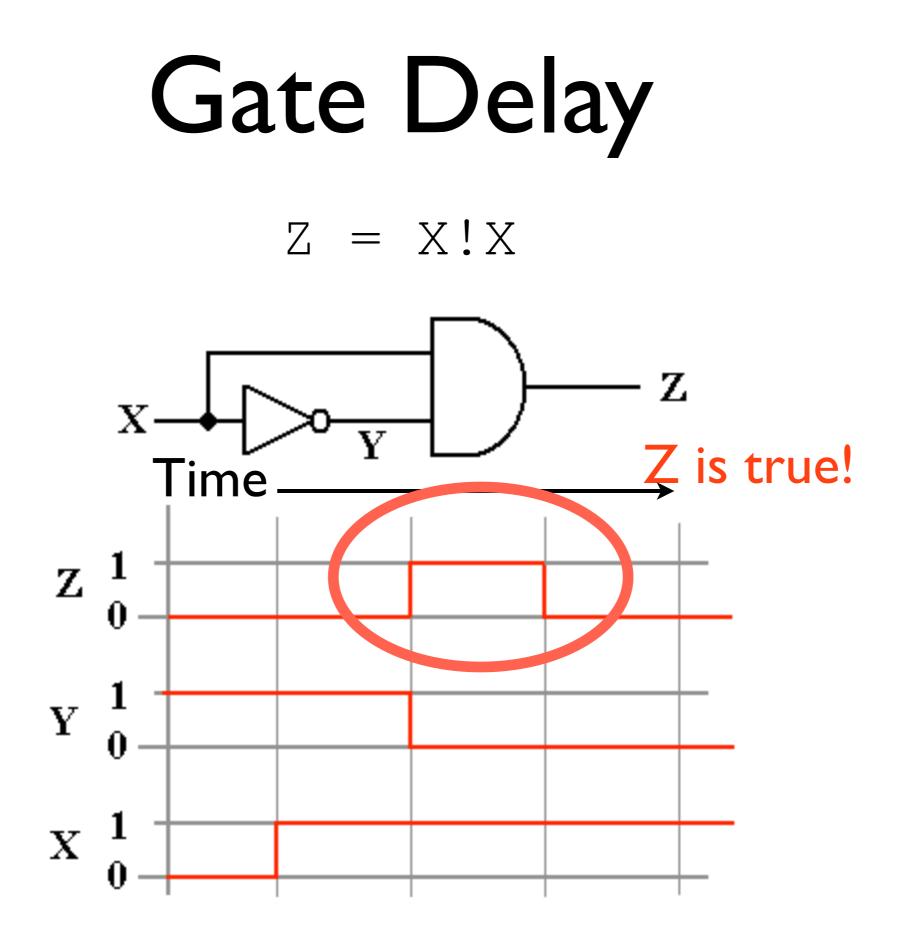

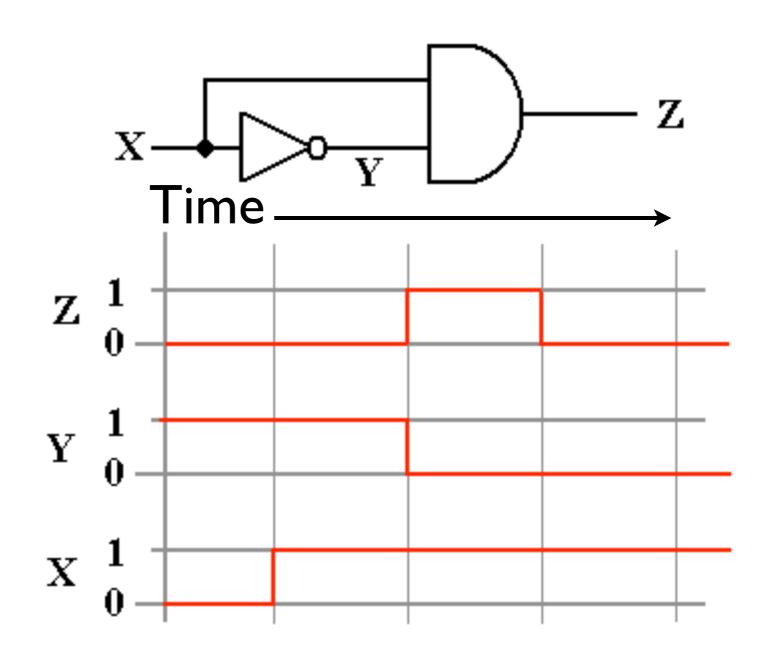

# Gate Delay

Z = X ! X

### Solution

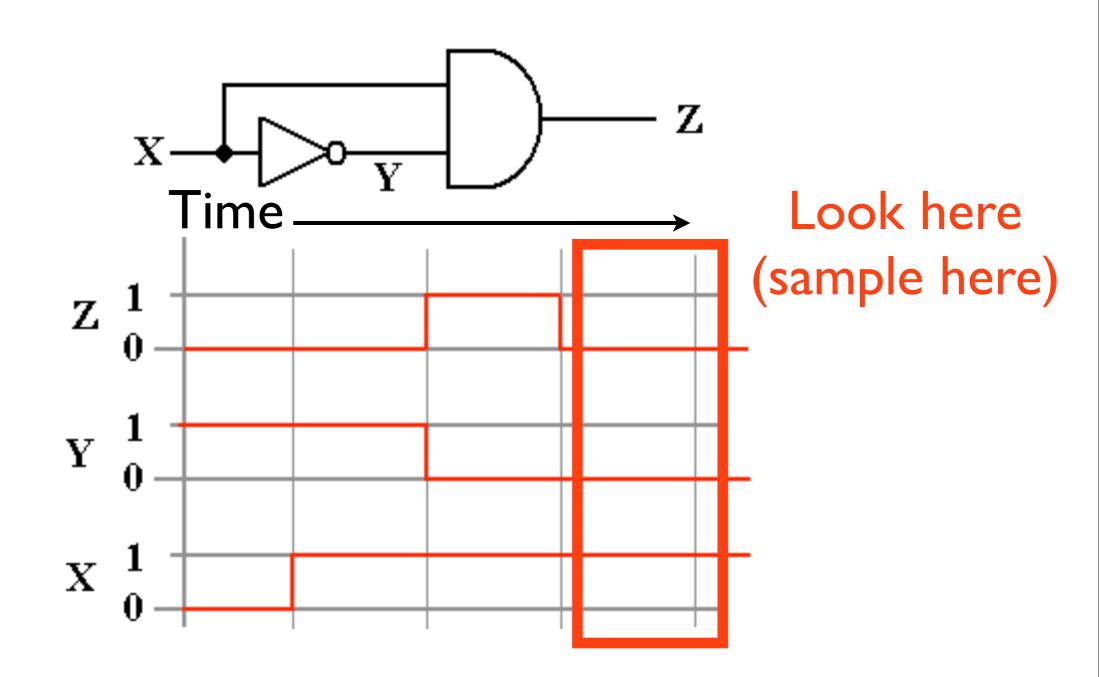

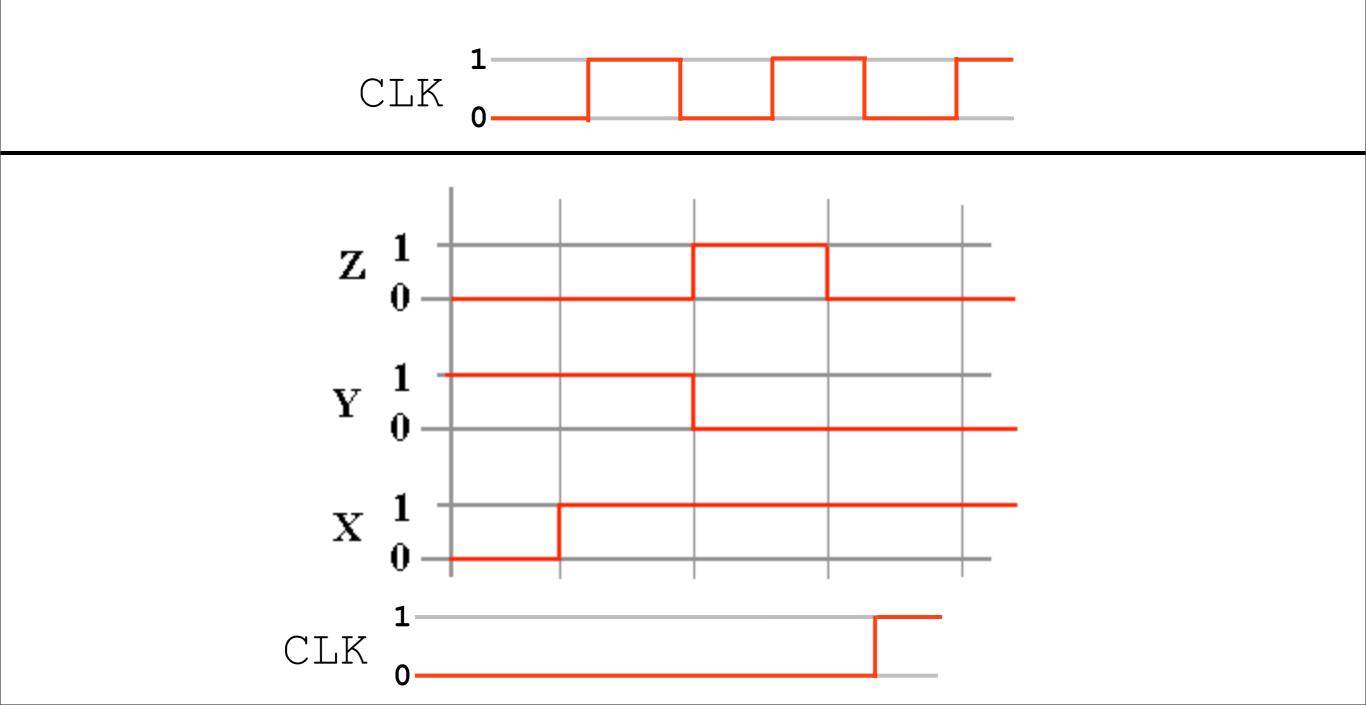

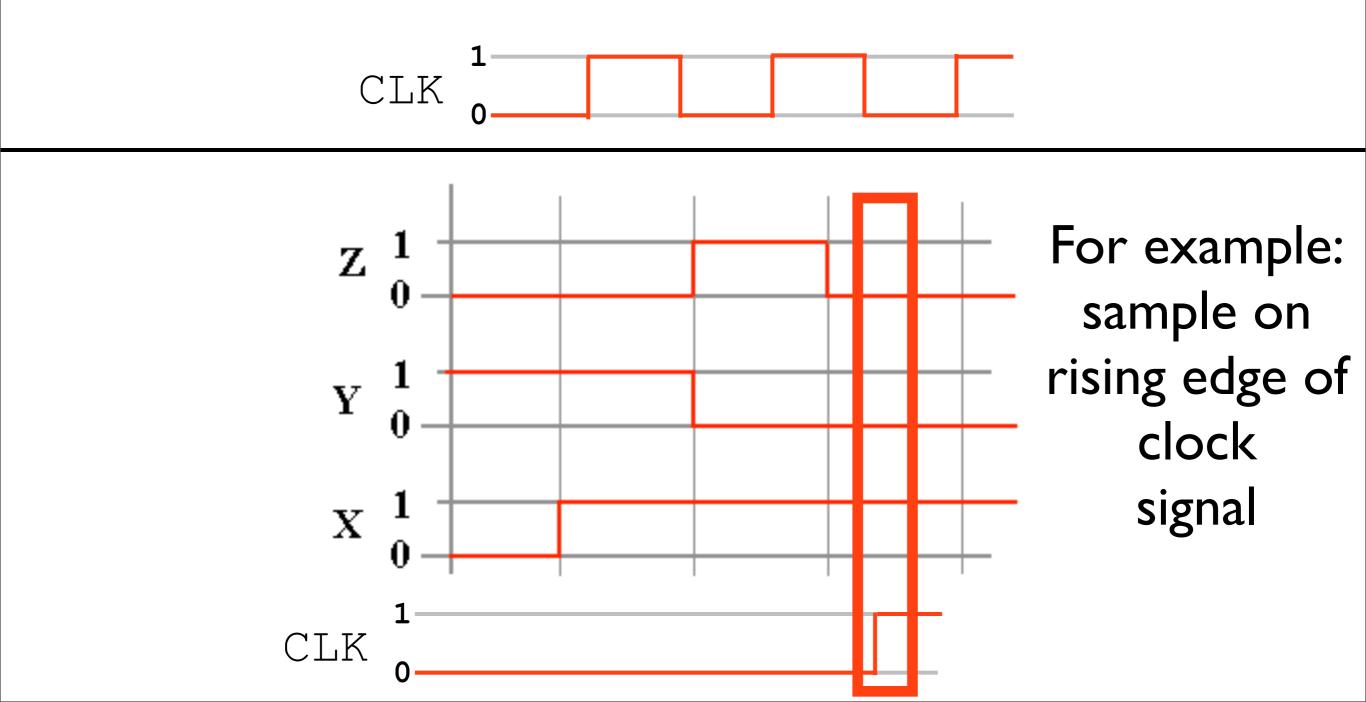

Only look at the outputs at preset intervals. Space the intervals so the circuit will always be stable by that point.

### Solution

Only look at the outputs at preset intervals. Space the intervals so the circuit will always be stable by that point.

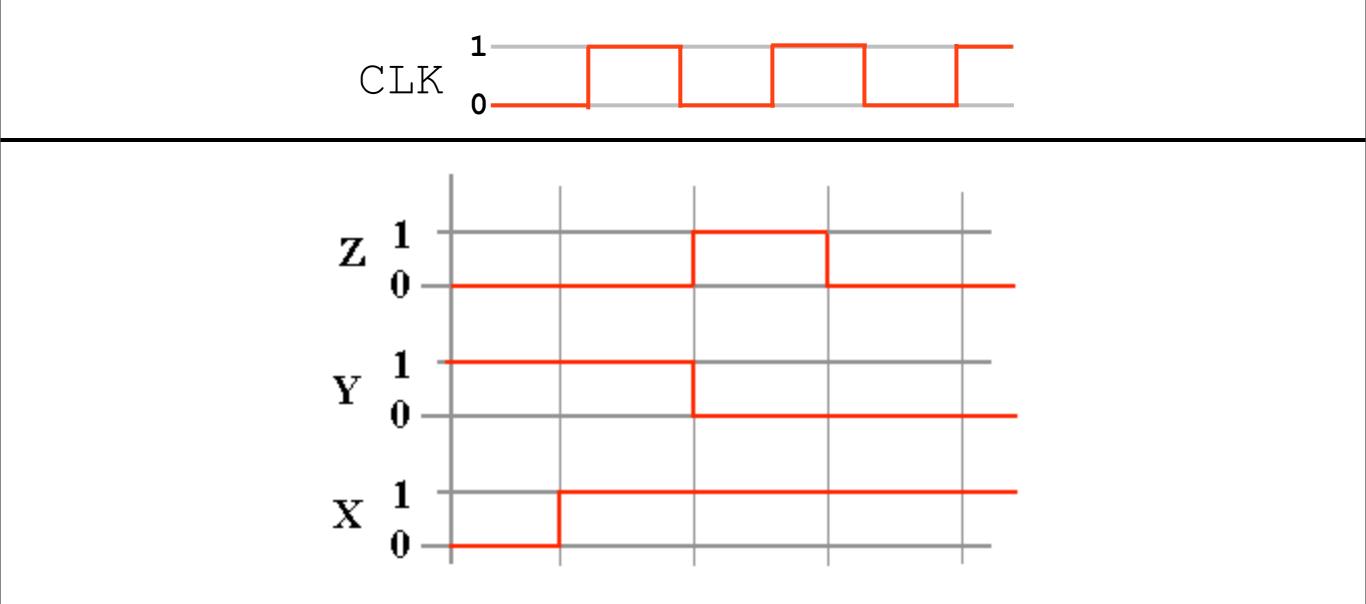

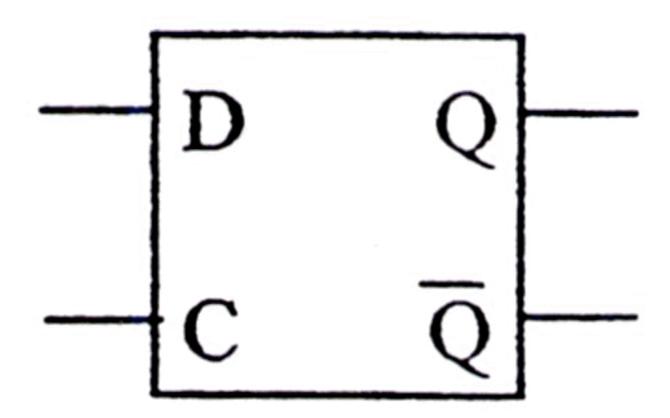

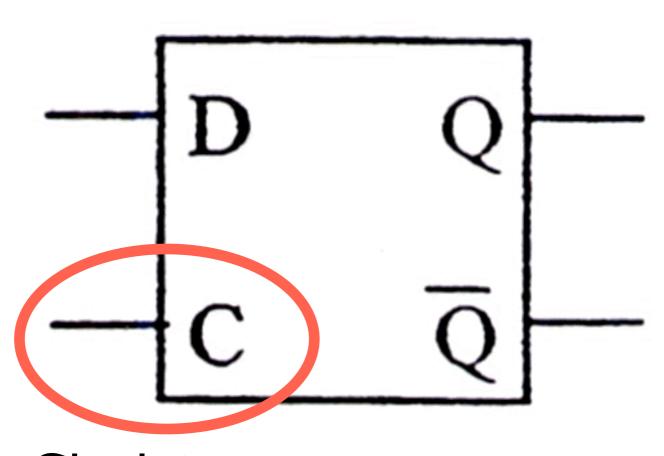

# D flip-flop

# D flip-flop

Clock input. This could be triggered on the rising edge, depending on the component